组合逻辑与时序逻辑

数字电子技术是现代技术进步的基础。数字设备是用布尔逻辑原理创建的。布尔逻辑根据输出的性质分为组合逻辑和时序逻辑。每种类型的逻辑都可以用来实现今天使用的不同数字元件。

组合逻辑

在组合逻辑中,输出只是当前输入的函数。输出独立于先前的输出,因此有时称为时间无关逻辑。

组合逻辑用于对二进制输入信号和二进制数据进行布尔运算。CPU的算术和逻辑单元对数据串执行组合运算。半加器、全加器、多路复用器、解复用器、译码器和编码器也基于组合逻辑设计。

时序逻辑

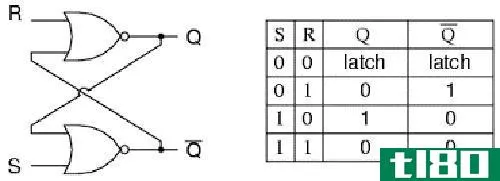

时序逻辑是布尔逻辑的一种形式,其输出是当前输入和过去输出的函数。在大多数情况下,输出信号作为新的输入反馈到电路中。序列逻辑用于设计和构建有限状态机。时序逻辑的基本实现是触发器。触发器的设计是为了保持系统的状态,因此,被认为是一个基本的存储元件。

时序逻辑又分为同步逻辑和异步逻辑。在同步逻辑中,通过提供给电路中每个触发器的振荡信号循环地重复逻辑操作。这个信号,通常被称为时钟脉冲,为一个单一的操作激活逻辑电路。

同步逻辑的主要优点是它的简单性。同步逻辑的主要缺点是可用的时钟速度有限,并且每个触发器都需要一个时钟信号。结果,同步电路的速度受到限制,当信号分配到每个触发器元件时,会出现能量损耗。

在异步逻辑中,所有的触发器都不是在同一个周期内时钟的。相反,每个触发器都是通过主时钟信号或另一个触发器的输出来计时的。因此,异步逻辑电路的速度远高于同步电路。尽管异步逻辑是有效的,但它们很难设计和实现,如果两个信号重叠,则会产生问题。

组合逻辑和顺序逻辑有什么区别?

•组合逻辑仅使用当前输入来确定输出,而顺序逻辑使用现有输入和先前输出来确定当前输入。

•组合逻辑用于实现基本布尔运算,而序列逻辑用于创建内存元素。